# Pontificia Universidad Javeriana

MASTER THESIS WORK

# DC/DC High Voltage Multilevel Converter in Double Ladder Topology (Convertidor multinivel DC-DC de alto voltaje en topología escalera doble)

Author: Eng. Andrés Mauricio López Canón

Directors: Eng. Diego Alejandro Patino Guevara, Ph. D. Eng. Rafael Fernando Díez Medina, Ph. D.

January 17, 2012

# Contents

| 1                                                                                       | Intr | roduction                                                                               | 1  |  |  |  |

|-----------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------|----|--|--|--|

| 2 Analysis and Comparison of Three Topologies of the Ladd<br>Multilevel DC/DC Converter |      |                                                                                         |    |  |  |  |

|                                                                                         | 2.1  | Introduction                                                                            | 5  |  |  |  |

|                                                                                         | 2.2  | Classical ladder topology (CLT)                                                         | 6  |  |  |  |

|                                                                                         |      | 2.2.1 Basic Cell of the ladder topology                                                 | 6  |  |  |  |

|                                                                                         |      | 2.2.2 Calculation of N and $R_{out}$ for $N_c$ cells                                    | 8  |  |  |  |

|                                                                                         | 2.3  | Symmetric Ladder Topology (SLT)                                                         | 10 |  |  |  |

|                                                                                         |      | 2.3.1 Calculation of N and $R_{out}$ for $N_c$ cells                                    | 11 |  |  |  |

|                                                                                         | 2.4  | Double Ladder Topology (DLT)                                                            | 13 |  |  |  |

|                                                                                         |      | 2.4.1 Calculation of $N$ and $R_{out}$ for $N_c$ cells                                  | 14 |  |  |  |

|                                                                                         | 2.5  | Topology comparison                                                                     | 15 |  |  |  |

|                                                                                         | 2.6  | Implementation and Experimental Results                                                 | 16 |  |  |  |

|                                                                                         |      | 2.6.1 Experimental set-up                                                               | 16 |  |  |  |

|                                                                                         |      | 2.6.2 Influence of the capacitor                                                        | 16 |  |  |  |

|                                                                                         |      | 2.6.3 Experimental results                                                              | 16 |  |  |  |

|                                                                                         |      | 2.6.4 Topology comparison                                                               | 17 |  |  |  |

|                                                                                         | 2.7  | Conclusions                                                                             | 18 |  |  |  |

| 3                                                                                       | An   | Equivalent Continuous Model for Switched Systems                                        | 21 |  |  |  |

|                                                                                         | 3.1  |                                                                                         | 21 |  |  |  |

|                                                                                         | 3.2  | Classical Average Model and Problem Formulation                                         | 22 |  |  |  |

|                                                                                         | 3.3  | General Equivalent Continuous Model                                                     | 23 |  |  |  |

|                                                                                         |      | 3.3.1 Model                                                                             | 23 |  |  |  |

|                                                                                         |      | 3.3.2 Linearization                                                                     | 26 |  |  |  |

|                                                                                         | 3.4  | <i>RMS</i> Value                                                                        | 27 |  |  |  |

|                                                                                         | 3.5  | Two sub models case example                                                             | 27 |  |  |  |

|                                                                                         |      | 3.5.1 Classical average model                                                           | 28 |  |  |  |

|                                                                                         |      | 3.5.2 General equivalent continuous model                                               | 29 |  |  |  |

|                                                                                         |      | 3.5.3 Linearization                                                                     | 29 |  |  |  |

|                                                                                         |      | 3.5.4 <i>RMS</i>                                                                        | 31 |  |  |  |

|                                                                                         | 3.6  | Conclusion                                                                              | 31 |  |  |  |

| 4                                                                                       |      | nparison of Robust Control Laws for a DC/DC Classical<br>der Multilevel Converter (CLT) | 33 |  |  |  |

|                                                                                         | 4.1  |                                                                                         | 33 |  |  |  |

|                                                                                         | 4.2  | Classical Ladder Multilevel converter CLT                                               | 33 |  |  |  |

|    |                                                           | 4.2.1 Model parameters                                         | 34        |  |  |  |  |  |  |

|----|-----------------------------------------------------------|----------------------------------------------------------------|-----------|--|--|--|--|--|--|

|    | 4.3                                                       | Steady State Analysis                                          | 34        |  |  |  |  |  |  |

|    | 4.4                                                       | Masks                                                          | 36        |  |  |  |  |  |  |

|    |                                                           | 4.4.1 Uncertainty masks                                        | 36        |  |  |  |  |  |  |

|    |                                                           | 4.4.2 Performance masks                                        | 37        |  |  |  |  |  |  |

|    | 4.5                                                       | Design of the Control law                                      | 38        |  |  |  |  |  |  |

|    |                                                           | 4.5.1 Classical controller                                     | 38        |  |  |  |  |  |  |

|    |                                                           | 4.5.2 Robust controllers                                       | 38        |  |  |  |  |  |  |

|    | 4.6                                                       | Simulation Results                                             | 41        |  |  |  |  |  |  |

|    |                                                           | 4.6.1 Load perturbation $+50\Omega$                            | 42        |  |  |  |  |  |  |

|    |                                                           | 4.6.2 Load perturbation $-50\Omega$                            | 42        |  |  |  |  |  |  |

|    | 4.7                                                       | Conclusions                                                    | 43        |  |  |  |  |  |  |

| 5  | Lad                                                       | lder Multilevel Converter Analysis Using a New Equivalent      |           |  |  |  |  |  |  |

|    |                                                           |                                                                | <b>45</b> |  |  |  |  |  |  |

|    | 5.1                                                       | Introduction                                                   | 45        |  |  |  |  |  |  |

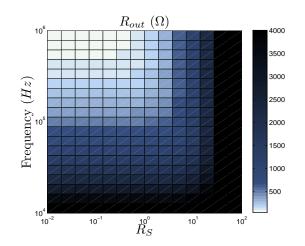

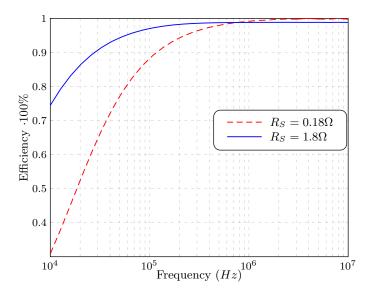

|    | 5.2                                                       | CLT Analysis                                                   | 46        |  |  |  |  |  |  |

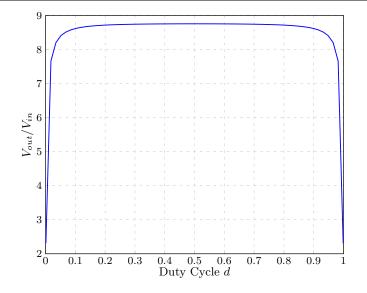

|    | 5.3                                                       | DLT Analysis                                                   | 48        |  |  |  |  |  |  |

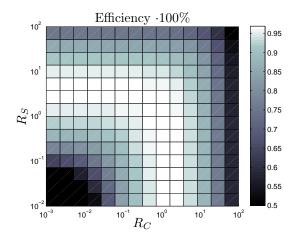

|    |                                                           | 5.3.1 Duty Cycle of maximum gain                               | 49        |  |  |  |  |  |  |

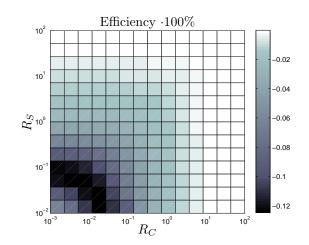

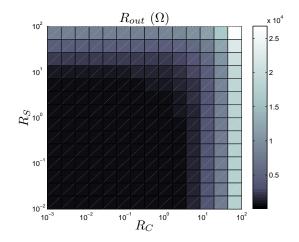

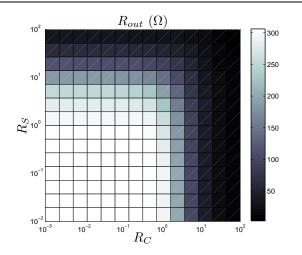

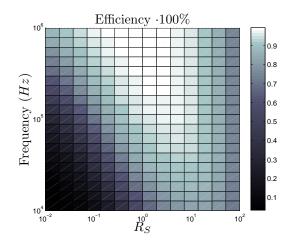

|    |                                                           | 5.3.2 Efficiency                                               | 50        |  |  |  |  |  |  |

|    |                                                           | 5.3.3 Duty Cycle effect                                        | 53        |  |  |  |  |  |  |

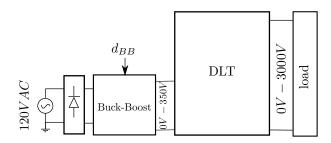

|    |                                                           | 5.3.4 Converter implementation                                 | 54        |  |  |  |  |  |  |

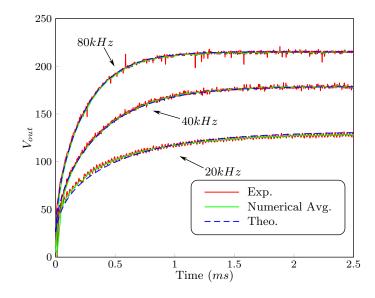

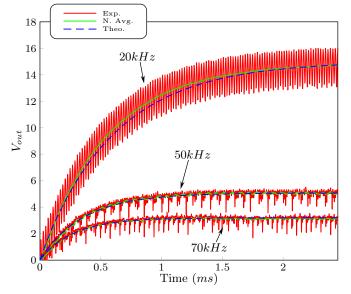

|    | 5.4                                                       | Experimental Results                                           | 54        |  |  |  |  |  |  |

|    | 5.5                                                       | Conclusions                                                    | 55        |  |  |  |  |  |  |

| 6  | Modeling and Control Design of a Double Ladder Multilevel |                                                                |           |  |  |  |  |  |  |

|    | Cor                                                       | nverter for a Glow Discharge Application                       | <b>57</b> |  |  |  |  |  |  |

|    | 6.1                                                       | Introduction                                                   | 57        |  |  |  |  |  |  |

|    | 6.2                                                       | Robust Control Design                                          | 57        |  |  |  |  |  |  |

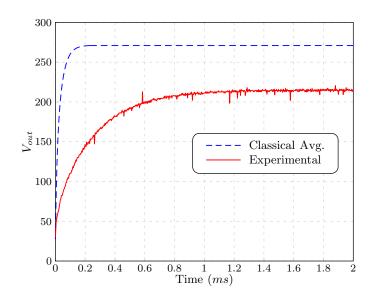

|    |                                                           | 6.2.1 Classical average model problem                          | 57        |  |  |  |  |  |  |

|    |                                                           | 6.2.2 Glow discharge control using the General Equivalent Con- |           |  |  |  |  |  |  |

|    |                                                           | tinuous Model                                                  | 59        |  |  |  |  |  |  |

|    | 6.3                                                       | Implementation                                                 | 60        |  |  |  |  |  |  |

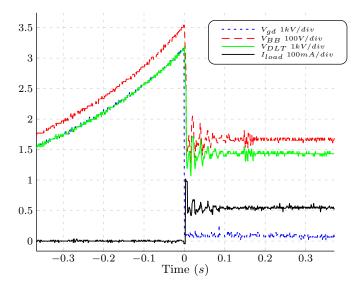

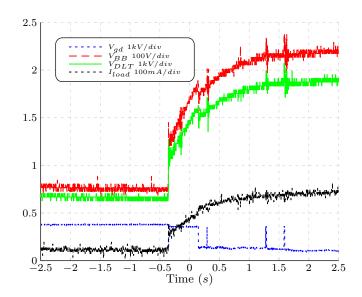

|    | 6.4                                                       | Experimental Results                                           | 60        |  |  |  |  |  |  |

|    |                                                           | 6.4.1 Model Validation                                         | 60        |  |  |  |  |  |  |

|    |                                                           | 6.4.2 Controller                                               | 63        |  |  |  |  |  |  |

|    | 6.5                                                       | Conclusions                                                    | 65        |  |  |  |  |  |  |

| Bi | ibliog                                                    | graphy                                                         | <b>74</b> |  |  |  |  |  |  |

# Chapter 1

# Introduction

Classical switched power converters have some limitations in high voltage applications. They commonly require switching and passive energy storage components with operating voltages higher than the output voltage [1],[2]. With the increase of high voltage applications (several kilovolts), these converters, such as boost and buck, need high voltage and fast switching components, which are not fabricated with current technologies.

At the beginning of the 1990s, a new breed of power converters, called multilevel converters, appeared; these converters solved the problem of the high voltage on classical converters using a series connection of several basic cells [3], [4], [5], [6]. This technique allows the converter to manage high voltage using low voltage components. Multilevel converters have shown a good performance in high power applications [7], [8] for DC/DC [9], [10], [11] and DC/AC [12], [13], [14] conversion.

Within the multilevel topologies, there are some that use only capacitive storage elements such as Flying Capacitors and Ladder. Despite this type of converters, called switched capacitors converters, are widely used nowadays [15], [16], [17], due to its principle of functionality, they produce undesirable losses due to the capacitors charge process [18], [19]. Moreover, conduction and switching losses in the semiconductor devices and losses in the ESR of the capacitors occur because of the current spikes when two capacitors are interconnected [20], [21], [22], [23]. In [24], these current spikes are reduced using resonant techniques adding a small inductance in series with the capacitors, minimizing also the switching losses. Nevertheless, at high frequencies these inductors contribute to the converter losses [21].

Average models are widely used to obtain equivalent linear models of hybrid and non linear systems [25]. This eases the design of a control law allowing to use classical control design techniques [26, 27]. One of the possible applications for the average model is to find equilibrium points and admissible references in switched systems when the switching devices are assumed to be ideal [28].

The averaging technique is commonly used in power electronics (switching power supplies). It allows to remove the nonlinearities of the switching devices and obtain equivalent linearized models [29, 1, 30, 31, 32, 33, 34, 35]. Indeed, classical average models work under the assumption of slow state space dynamics compared to the period of one switching cycle. Although the classical technique

is simple, the assumptions of slow switching are not always fulfilled, leading to inaccurate models. In [36] several modeling techniques, such as Fourier series [37] and discrete time models [38] are reviewed. Also in [39] and [40] some drawbacks of the classical average model are discussed and alternative methods are mentioned. A modeling technique using series expansion, explained in more detail in [41, 42], corrects the error of the classical average model, nevertheless, it requires the assumption of a triangle ripple function in order to correctly estimate the average; this technique is also applied to a current control power converter in [43].

This document is organized as follows

#### Chapter 2

In this chapter three DC/DC ladder multilevel converters are compared. The first one is the classical ladder topology and the two other topologies presented are based on the classical one. A mathematical calculation of the output resistance and the gain of the converter as a function of the number of levels is carried out for the three topologies in order to estimate the voltage drop due to the output current. These calculations are validated with simulations and experimental results. Finally, the behavior of the three topologies is compared through experimental tests. Results show higher performance for the presented converters compared to the classical ladder.

Papers derived from this chapter: [44], [45], [46]

### Chapter 3

In this chapter, a new technique of continuous modeling for switched systems represented as piecewise LTI systems over the state space variables is proposed. A procedure to calculate the Root Mean Square (RMS) value based on this technique is also enounced. In order to validate these models, a numerical example with a DC/DC power converter is used. The calculations of the state space matrices using the proposed model are performed and compared with the classical average model, and the time response is contrasted with simulations demonstrating its effectiveness. A linearized model of the proposed continuous model is obtained numerically due to its analytical complexity, and the frequency response for both models is also analyzed. The calculation of the RMS is validated with simulations.

Paper derived from this chapter: [47]

#### Chapter 4

In this chapter, different control methods for a classical ladder multilevel converter (CLT) (three levels) are evaluated. An analysis of the classical average model allows to chose an operation point. With the set of operation points, an uncertain model of the converter is constructed. Moreover, perturbation variables and performance masks are also defined. All this information is used to design an  $H_{\infty}$  "mixed sensitivity" and  $\mu$  (DK) control laws for the uncertain case. The performance and robustness of the different controllers are compared through simulation with a classical *PI* control law.

Paper derived from this chapter: [48]

#### Chapter 5

The ladder multilevel converter uses switched capacitors in order to transfer energy between its input and its output. These types of converters have fast dynamics on each switching state compared to the switching frequency which produces model inaccuracies when the classical averaging modeling technique is applied. In this chapter two ladder multilevel converters (classical ladder topology (CLT) and double ladder topology (DLT)) are analyzed using a new averaging modeling technique. The CLT is analyzed using the classical and the new technique and the results are compared in order to illustrate the need of the procedure. Finally, a DLT converter of eight cells is analyzed and optimized for a glow discharge applications and some efficiency results are validated experimentally.

Paper derived from this chapter: [49]

## Chapter 6

An accurate modeling technique is important in order to design a model-based control law. For switched system the classical state space averaging is a widely used modeling technique. However, this technique works under the assumption of slow dynamics of the state space variables. For certain power converters, such as switched capacitor converters, this assumption is not satisfied. In this chapter, comparisons of stability of robust control laws designed with the classical average are carried out in order to illustrate the need of a more accurate modeling technique. A ladder multilevel converter is modeled and analyzed using a new modeling technique for switched systems and its effectiveness is validated with experimental measurements. A robust control law is designed for a glow discharge application and its performance is tested experimentally.

# Chapter 2

# Analysis and Comparison of Three Topologies of the Ladder Multilevel DC/DC Converter

# 2.1 Introduction

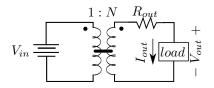

The equivalent circuit of a switched capacitor converter in steady state is illustrated in Fig. 2.1. This equivalent circuit consists of a DC/DC transformer with turns ratio N and an equivalent output resistance  $R_{out}$  which represents all the losses and the output voltage dropout [9].

Figure 2.1: Equivalent model of a switched capacitor converter

This chapter analyzes the classical ladder multilevel topology and two variations. A general mathematic expression of  $R_{out}$  for the three topologies as a function of the number of cells is derived. In [23], the calculation of  $R_{out}$  is based on a state space model, this requires the re-computation of the matrices when a new cell is added or removed. The method proposed in this chapter allows the calculation of  $R_{out}$  as a function of the number of cells and without the computation of the state space matrices. The analysis proposed is validated through simulation and with experimental measurements using a prototype circuit. Finally it is demonstrated which topology produces less output resistance.

# 2.2 Classical ladder topology (CLT)

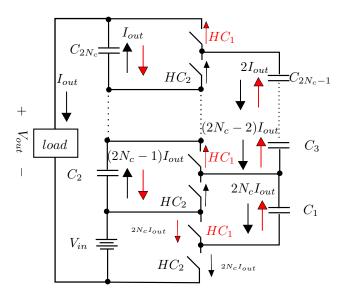

The classical ladder topology, shown in Fig. 2.2, is a simplified form of the flying capacitors topology. Both topologies (Classical ladder and Flying capacitors) are compared in [50]. The simplicity of the ladder topology is demonstrated since it requires less control signals an less switching and capacitive components [51]. As in [44], the converters studied in this work are analyzed as voltage elevators. However, since these converters are bidirectional [52], the analysis can be extended to step-down applications.

This topology requires only two control signals,  $HC_1$  and its complementary  $HC_2$ . These control signals have a constant duty cycle d equal to 50%, leading to an ideal output voltage with  $N_c$  cells of

$$V_{out} = (N_c + 1)V_{in}$$

(2.1)

and the number of necessary capacitors  $N_{Cap}$  and switches  $N_S$ , as follows

$$N_{Cap} = 2N_c$$

$$N_S = 2N_c + 2$$

(2.2)

Figure 2.2: DC/DC voltage multilevel elevator in CLT with  $N_c$  cells.  $HC_1$  denotes the half-cycle 1 and  $HC_2$  the half-cycle 2. Average currents are shown during each half-cycle. The current through the switches is  $2I_{out}$  except for those at the bottom cell.

The analysis of this topology is performed over its basic cell, shown in Fig. 2.3, without loss of generality

## 2.2.1 Basic Cell of the ladder topology

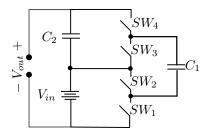

The basic cell of the ladder topology in Fig. 2.3 consists of two capacitive elements  $(C_1 \text{ and } C_2)$  and four switching components  $(SW_1, SW_2, SW_3 \text{ and } C_2)$

$SW_4$ ). When  $SW_1$  and  $SW_3$  are ON, the input voltage source  $V_{in}$  charges the capacitor  $C_1$ . In the other half cycle, with  $SW_2$  and  $SW_4$  ON, the capacitor  $C_1$  charges the capacitor  $C_2$  leading, in an ideal case, to  $V_{out} = 2V_{in}$

Figure 2.3: Basic cell of the ladder topology

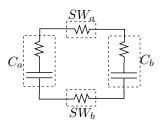

The connection between capacitors, illustrated in Fig. 2.4, are affected by the ON resistance of the switches and the ESR of each capacitor, producing voltage drops. Furthermore, the time constant of the equivalent circuit  $(\tau)$ , which depends of the capacitance and resistance values, affects the current waveform on the capacitors: a large  $\tau$  produces a square waveform, and a small  $\tau$  produces an exponential waveform. These waveforms are illustrated in Fig. 2.5.

It is important to mention that when the equivalent  $\tau$  is small compared with the switching period, the dynamic models of [31] can not produce an accurate model, because the conditions in [53] are not satisfied. However, alternative methods such as discrete time modeling can be used [54].

Figure 2.4: Connection between capacitors on a half-cycle

In steady state, the charge in the capacitor must be balanced, thus the average current in one switching period must be 0. In Fig. 2.5 both waveforms have the same average on each half cycle and 0 in the whole switching period, The exponential waveform has clearly higher spikes and therefore, a higher RMS value.

Figure 2.5: Current waveform for different  $\tau$  values

This basic cell is the same for all the structures studied in this chapter.

# **2.2.2** Calculation of N and $R_{out}$ for $N_c$ cells

In order to evaluate the voltage drop due to the load current, it is necessary to calculate the output resistance  $R_{out}$  and obtain an expression which allows to scale the converter for design purposes. A mathematical analysis under the assumption of square current waveforms in the capacitors is performed in this section, considering two possible states.

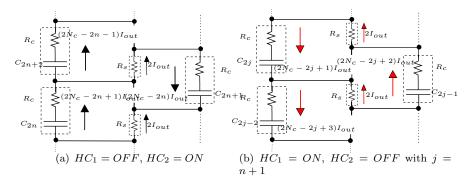

For the following procedures  $R_c$  represents the ESR of the capacitors and  $R_s$  represents the ON resistance of the switches. The generalized connection between capacitors is as shown in Fig. 2.6.

Figure 2.6: Generalized connection between capacitors on each half-cycle

#### State 1 ( $HC_1 = OFF$ and $HC_2 = ON$ )

It is necessary to calculate the voltage of the capacitor  $C_1$  in a different way than the voltage of the other capacitors since the current through the switches of the first cell is different compared to other cells, as seen in Fig. 2.2 (Note that the current of the switches connected to  $V_{in}$  is the same as for  $C_1$ ; for all the other cases, is the current difference of the capacitors connected to the switch, i.e.  $2I_{out}$ ). Therefore, this voltage is expressed as follows

$$V_{C_1} = V_{in} - 2I_{out}(N_c R_c + R_s(N_c + 1))$$

(2.3)

where  $N_c$  is the number of cells in the converter. In general, for this halfcycle the connection between capacitors is as shown in Fig. 2.6(a). Therefore, the voltage of the capacitor  $C_{2n+1}$  can be expressed in terms of voltage of the capacitor  $C_{2n}$  as follows:

$$V_{C_{2n+1}} = V_{C_{2n}} - I_{out}(4N_c + 1 - 4n)R_c$$

(2.4)

where  $n \in [1, N_c - 1]$ . The output voltage  $V_{out}$  during this half cycle is the sum of the voltages of the capacitors with even subindex  $(C_2, C_4, \ldots, C_{2N_c})$  plus  $V_{in}$  (see Fig. 2.2). Since each capacitor has an internal *ESR*, it is necessary to include its voltage drop. Therefore  $V_{out}$  can be expressed as

$$V_{out_1} = V_{in} + \left[\sum_{n=1}^{N_c - 1} \left(V_{C_{2n}} - (2N_c + 1 - 2n)I_{out}R_c\right)\right] + V_{C_{2N_c}} - I_{out}R_c$$

(2.5)

Note that the voltage drop in all the  $R_s$  resistances is cancelled, except at the bottom cell (2.3).

## State 2 ( $HC_1 = ON$ and $HC_2 = OFF$ )

Again, it is necessary to calculate the voltage of the capacitor  $C_2$  differently. This voltage can be expressed in terms of  $V_{C_1}$  as follows

$$V_{C_2} = V_{C_1} - I_{out}(2R_s(N_c + 1) + R_c(4N_c - 1))$$

(2.6)

for this state the connection between capacitors is as shown in Fig. 2.6(b). Therefore, the voltage of the capacitor  $V_{C_{2j}}$  can be expressed recursively as

$$V_{C_{2j}} = V_{C_{2j-1}} - I_{out} R_c (4N_c + 3 - 4j)$$

(2.7)

with j = n + 1. The output voltage, as in the previous case, can be expressed during this half cycle as

$$V_{out_2} = V_{in} + V_{C_2} + (2N_c - 1)I_{out}R_c + \left[\sum_{j=2}^{N_c} \left(V_{C_{2j}} + (2N_c - 1 - 2j)I_{out}R_c\right)\right]$$

(2.8)

As in state 1, voltage drop in  $R_s$  resistances is only seen at the bottom cell (2.6).

#### **Output Average Voltage**

Since the duty cycle is constant and equal to 50%, the average output voltage  $\overline{V_{out}}$  of the two previous cases is

$$\overline{V_{out}} = \frac{V_{out_1} + V_{out_2}}{2} = V_{in} + \sum_{m=1}^{N_c} V_{C_{2m}}$$

(2.9)

Note that the resistive drop is canceled. From (2.4) and (2.7) it can be obtained in terms of n

$$V_{C_{2n+2}} = V_{C_{2n}} - 4I_{out}R_c(2N_c - 2n)$$

(2.10)

The initial conditions for this difference equation are obtained from (2.3) and (2.6), where

$$V_{C_2} = V_{in} - I_{out} R_c (6N_c - 1) - 4I_{out} R_s (N_c + 1)$$

(2.11)

Solving the difference equation in (2.10), the voltage on the capacitors is

$$V_{C_{2m}} = V_{in} - 4I_{out}R_s(N_c + 1) - I_{out}R_c(2N_c(4m - 1) - 4m^2 + 4m - 1)$$

(2.12)

with  $m \in [1, N_c]$ . Using (2.9),  $\overline{V_{out}}$  can be calculated, resulting in

$$\overline{V_{out}} = V_{in} \underbrace{(N_c + 1)}_{N} - I_{out} \underbrace{\left[ 4N_c R_s (N_c + 1) + N_c R_c \frac{8N_c^2 + 6N_c + 1}{3} \right]}_{R_{out}}$$

(2.13)

# 2.3 Symmetric Ladder Topology (SLT)

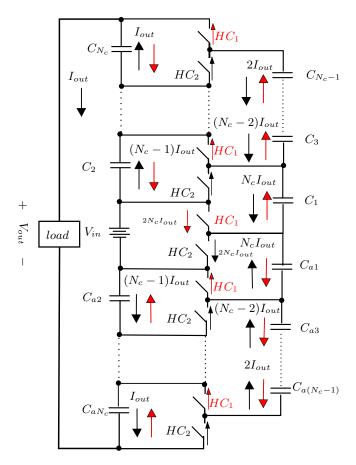

Fig. 2.7 shows the SLT. The functionality principle of this topology is the same as for CLT. It has two control signals,  $HC_1$  and its complementary  $HC_2$ , with duty cycle *d* equal to 50%. The number of cells  $N_c$  must be even. A similar topology is used in [55] to maintain voltage balance in the capacitors of a diodeclamped converter. However, it is not analyzed as a voltage elevator considering parasitic resistances.

The main difference of this topology is how the current is distributed through the circuit (see Fig. 2.7). The current in the capacitors is up to  $N_c I_{load}$  in contrast to  $2N_c I_{load}$  of the CLT.

Figure 2.7: SLT as a DC/DC voltage multilevel elevator with  $N_c$  cells.  $HC_1$  denotes the half-cycle 1 and  $HC_2$  the half-cycle 2. Average currents are shown during each half cycle. The current through the switches is  $2I_{out}$  except for those of the cell connected to the input voltage source  $V_{in}$ .

The number of necessary capacitors  $N_{Cap}$  and switches  $N_S$  for its implementation is

$$N_{Cap} = 2N_c$$

$$N_S = 2N_c + 2$$

(2.14)

One of the advantages of this topology is the interleaving between the upperhalf part and the lower-half part of the circuit. Notice how, in the same halfcycle, the current in the capacitors  $C_n$  flows in the opposite direction of the current in the capacitors  $C_{an}$ . This implies that the converter output voltage and its input current have a smaller ripple than in CLT [56], [57], [58], as it is analyzed in the next subsection.

# **2.3.1** Calculation of N and $R_{out}$ for $N_c$ cells

In an analogous procedure as in Section 2.2.2, in this section, the output resistance  $R_{out}$  for the topology B is calculated under the assumption of square current waveforms.

## State 1 ( $HC_1 = OFF$ and $HC_2 = ON$ )

The voltage of the capacitor  $C_1$  for this topology is

$$V_{C_1} = V_{in} - I_{out}(N_c R_c + 2R_s(N_c + 1))$$

(2.15)

Where  $N_c$  is the number of cells in the converter and must be even. The recursive expression of the capacitors voltage can be written as follows (see Fig. 2.6(a))

$$V_{C_{2n+1}} = V_{C_{2n}} - I_{out}(2N_c + 1 - 4n)R_c$$

(2.16)

where  $n \in [1, N_c/2 - 1]$ .

It is necessary to compute the voltage in the capacitors  $C_{an}$  to calculate the output voltage for this half-cycle. Thus, the voltage of the capacitor  $C_{a2}$  is

$$V_{C_{a2}} = V_{C_{a1}} - I_{out}(2R_s(N_c + 1) + R_c(2N_c - 1))$$

(2.17)

and the recursive expression for the voltage of the capacitors  $C_{aj}$  is (see Fig. 2.6(b))

$$V_{C_{a(2j)}} = V_{C_{a(2j-1)}} - I_{out} R_c (2N_c + 3 - 4j)$$

(2.18)

with j = n + 1. Then the output voltage  $V_{out}$  for this half-cycle is

$$V_{out_{1}} = V_{in} + \left[\sum_{n=1}^{N_{c}/2-1} (V_{C_{2n}} - (N_{c} + 1 - 2n)I_{out}R_{c})\right] + (V_{C_{N_{c}}} - I_{out}R_{c}) + (V_{C_{a2}} + (N_{c} - 1)I_{out}R_{c}) + \left[\sum_{j=2}^{N_{c}/2} (V_{C_{a(2j)}} + (N_{c} - 1 - 2j)I_{out}R_{c})\right]$$

(2.19)

Note that in (2.19), the resistive voltage drop due to  $R_c$  is canceled, leading to

$$V_{out_1} = V_{in} + \sum_{n=1}^{N_c/2-1} (V_{C_{2n}}) + V_{C_{N_c}} + V_{C_{a2}} + \sum_{j=2}^{N_c/2} (V_{C_{a(2j)}})$$

(2.20)

# State 2 ( $HC_1 = ON$ and $HC_2 = OFF$ )

The voltage of the capacitor  $C_2$  is

$$V_{C_2} = V_{C_1} - I_{out}(2R_s(N_c + 1) + R_c(2N_c - 1))$$

(2.21)

The recursive expression for the voltage of the capacitors  $C_j$ , as in the previous cases, for this half cycle is

$$V_{C_{2j}} = V_{C_{2j-1}} - I_{out} R_c (2N_c + 3 - 4j)$$

(2.22)

with j = n + 1.

Again it is necessary to compute the voltage of the capacitors  $C_{an}$ . Then the voltage of the capacitor  $C_{a1}$  is

$$V_{C_{a1}} = V_{in} - I_{out}(N_c R_c + 2R_s(N_c + 1))$$

(2.23)

and the recursive expression for the voltage of the capacitors  $C_{an}$  can be expressed as

$$V_{C_{a(2n+1)}} = V_{C_{a(2n)}} - I_{out}(2N_c + 1 - 4n)R_c$$

(2.24)

For this half-cycle, the output voltage can be written as follows

$$V_{out_{2}} = V_{in} + \left[\sum_{n=1}^{N_{c}/2-1} \left(V_{C_{a(2n)}} + (N_{c}+1-2n)I_{out}R_{c}\right)\right] \\ + \left(V_{C_{aN_{c}}} - I_{out}R_{c}\right) + \left(V_{C_{2}} + (N_{c}-1)I_{out}R_{c}\right) \\ + \left[\sum_{j=2}^{N_{c}/2} \left(V_{C_{2j}} + (N_{c}-1-2j)I_{out}R_{c}\right)\right]$$

(2.25)

Again, the resistive voltage drop due to  $R_c$  is canceled, and the output voltage can be reduced to

$$V_{out_2} = V_{in} + \sum_{n=1}^{N_c/2-1} \left( V_{C_{a(2n)}} \right) + V_{C_{aN_c}} + V_{C_2} + \sum_{j=2}^{N_c/2} \left( V_{C_{2j}} \right)$$

(2.26)

#### **Output Average Voltage**

From (2.16), (2.22), (2.17) and (2.24) it can be obtained in terms of n

$$V_{C_{2n+2}} = V_{C_{a(2n+2)}} = V_{C_{2n}} - 4I_{out}R_c(N_c - 2n)$$

(2.27)

besides  $V_{C_{a(2n)}} = V_{C_{2n}} = V_{C_{2m}}$  with  $m \in [1, N_c/2]$ . Therefore, the average output voltage  $\overline{V_{out}}$  on the two half-cycles is

$$\overline{V_{out}} = \frac{V_{out_1} + V_{out_2}}{2} = V_{in} + 2\sum_{m=1}^{N_c/2} V_{C_{2m}}$$

(2.28)

Solving the difference equation in (2.27), the voltage of the capacitors is

$$V_{C_{2m}} = V_{in} - 4I_{out}R_s(N_c + 1) - I_{out}R_c(N_c(4m - 1) - 4m^2 + 4m - 1)$$

(2.29)

then, using (2.28),  $\overline{V_{out}}$  can be expressed as follows

$$\overline{V_{out}} = V_{in} \underbrace{(N_c + 1)}_{N} - I_{out} \underbrace{\left[ 4N_c R_s (N_c + 1) + N_c R_c \frac{2N_c^2 + 3N_c + 1}{3} \right]}_{R_{out}}$$

(2.30)

Table 2.1: Topology comparison

| Topology | $N_{Cap}$ | $N_S$        | Ν           | $R_{out}$                                            | Ripple Cancelation |

|----------|-----------|--------------|-------------|------------------------------------------------------|--------------------|

| CLT      | $2N_c$    | $2N_{c} + 2$ | $N_{C} + 1$ | $4N_cR_s(N_c+1) + N_cR_c\frac{8N_c^2 + 6N_c + 1}{2}$ | No                 |

| SLT      | $2N_c$    | $2N_c + 2$   | $N_c + 1$   | $4N_cR_s(N_c+1) + N_cR_c\frac{2N_c^2+3N_c+1}{2}$     | Yes                |

| DLT      | $2N_c$    | $2N_{c} + 4$ | $N_{C} + 1$ | $2N_cR_s(N_c+2) + N_cR_c\frac{2N_c^2 + 3N_c + 1}{3}$ | Yes                |

# 2.4 Double Ladder Topology (DLT)

Fig. 2.8 shows the DLT, its principle of functionality is the same of the two previous topologies and, as for SLT, the number of cells  $N_c$  must be even

Figure 2.8: DLT of a DC/DC voltage multilevel elevator with  $N_c$  cells.  $HC_1$  denotes the half-cycle 1 and  $HC_2$  the half-cycle 2. Average currents are shown during each half-cycle. The current trough the switches is  $2I_{out}$  except for those of the cell connected to the input voltage source  $V_{in}$

For its implementation, the number of necessary capacitors  $N_{Cap}$  and switches  $N_S$  is  $N_{Cap} = 2N_c$

$$C_{ap} = 2N_c$$

$$N_S = 2N_c + 4$$

(2.31)

This topology requires the same number of capacitors and two more switching devices in comparison with the two previous topologies. This topology has the same interleaving properties as SLT if the control signals are distributed as shown in Fig. 2.8, producing a small output voltage ripple and small input current ripple.

# **2.4.1** Calculation of N and $R_{out}$ for $N_c$ cells

The calculation of N and  $R_{out}$  for this topology is the same as for SLT. The difference between this topology and SLT is how the first capacitors are charged, therefore, these voltages  $(V_{C_1}, V_{C_2}, V_{C_{a1}} \text{ and } V_{C_{a2}})$  need to be recalculated.

This section illustrates the calculation of the topology parameters using the results of SLT.

## State 1 ( $HC_1 = OFF$ and $HC_2 = ON$ )

The voltage of the capacitor  $C_1$  and  $C_{a2}$  is

$$V_{C_1} = V_{in} - I_{out}(N_c R_c + R_s(N_c + 2))$$

(2.32)

$$V_{C_{a2}} = V_{C_{a1}} - I_{out}(R_c(2N_c+1) + R_s(N_c+2))$$

(2.33)

The recursive expression of the voltage of the capacitors as well as the output voltage for this half cycle are the same as in (2.16), (2.18) and (2.20) respectively.

# State 2 ( $HC_1 = ON$ and $HC_2 = OFF$ )

The voltage of the capacitor  $C_2$  and  $C_{a1}$  is

$$V_{C_2} = V_{C_1} - I_{out}(R_s(N_c + 2) + R_c(2N_c + 1))$$

(2.34)

$$V_{C_{a1}} = V_{in} - I_{out}(R_s(N_c + 2) + R_c N_c)$$

(2.35)

Again, the recursive expression and the output voltage for this half cycle are the same as in (2.22), (2.24) and (2.26) respectively.

#### **Output Voltage Average**

The difference equation for the capacitor voltages is the same as in (2.27). In contrast with the previous topology, the initial conditions for this equation are derived from (2.32), (2.33), (2.34) and (2.33) leading to the following result

$$V_{C_{2m}} = V_{in} - 2I_{out}R_s(N_c + 2) - I_{out}R_c(N_c(4m - 1) - 4m^2 + 4m - 1)$$

(2.36)

then, using (2.28),  $\overline{V_{out}}$  is

$$\overline{V_{out}} = V_{in} \underbrace{(N_c + 1)}_{N} - I_{out} \underbrace{\left[ 2N_c R_s (N_c + 2) + N_c R_c \frac{2N_c^2 + 3N_c + 1}{3} \right]}_{R_{out}}$$

(2.37)

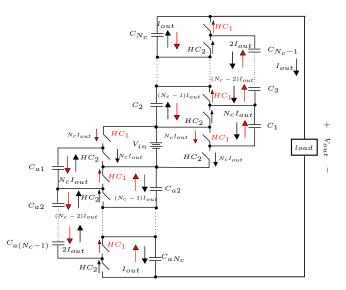

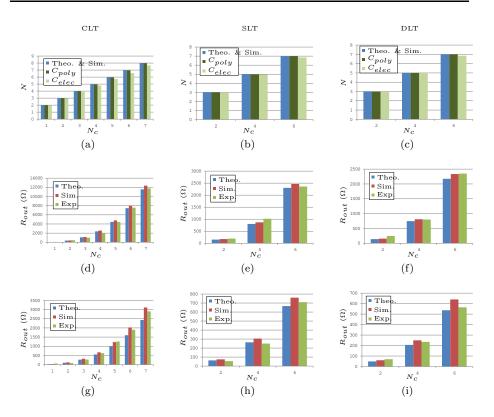

Figure 2.9: Comparison of theoretical, simulation and experimental results for CLT, SLT and DLT with capacitors  $C_{elec}$  and  $C_{poly}$  (a), (b), (c) Value of N without load for theoretical and simulation results, and experimental results for  $C_{poly}$  and  $C_{elec}$ ; (d), (e), (f) Theoretical, simulation and experimental results of output resistance  $R_{out}$  for different values of  $N_c$  using the capacitor  $C_{elec}$ ; (g), (h), (i) Theoretical, simulation and experimental results of output resistance  $R_{out}$  for different values of  $N_c$  using the capacitor  $C_{elec}$ ; (g), (h), (i) Theoretical, simulation and experimental results of output resistance  $R_{out}$  for different values of  $N_c$  using the capacitor  $C_{poly}$

# 2.5 Topology comparison

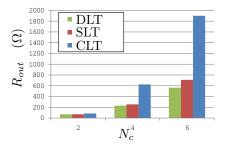

Table 2.1 shows a comparison between the three topologies analyzed. Electrical and hardware characteristics are taken into account. For example, Table 2.2 shows a numerical comparison with  $N_c = 6$ ,  $R_c = 2\Omega$  and  $R_s = 1.8\Omega$ . Although DLT uses two more switching components, it can be observed that this topology has the lowest output resistance  $R_{out}$ , up to 3 times smaller than for CLT, producing less voltage drop.

Table 2.2: Topology comparison with  $N_c = 6$ ,  $Rc = 2\Omega$  and  $R_s = 1.8\Omega$

| Topology | $N_{Cap}$ | $N_S$ | N | $R_{out}$    |

|----------|-----------|-------|---|--------------|

| CLT      | 12        | 14    | 7 | $1602\Omega$ |

| SLT      | 12        | 14    | 7 | $666\Omega$  |

| DLT      | 12        | 16    | 7 | $537\Omega$  |

# 2.6 Implementation and Experimental Results

# 2.6.1 Experimental set-up

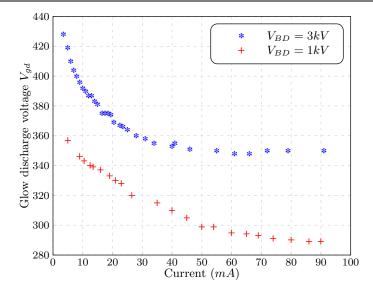

In order to validate the theoretical analysis carried out for the three topologies in the previous sections, and to test the performance of the converter for a future application in a 3000V, 100mA glow discharge; experimental measurements are taken. The measurements are made with an input voltage  $V_{in} = 300V$  and an output current  $I_{out} = 50mA$  and  $I_{out} = 100mA$ .

A P8NK100Z N-channel MOSFET is used as the switching component. This switch has a breakdown voltage of 1000V and an ON resistance  $R_s = 1.8\Omega$ .

For driving the *gate* control signals, four pulse transformers are employed, these transformers are built with 3000V isolation between each of its windings.

To evaluate the influence of the capacitor on the converter performance, two different capacitors are used as shown in Table 2.3.

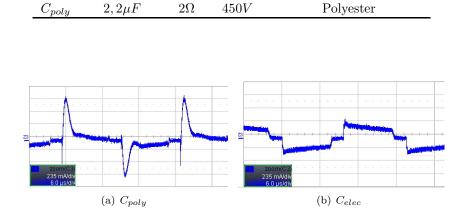

# 2.6.2 Influence of the capacitor

Capacitance

$1\mu F$

$C_{elec}$

The current waveform for each capacitor is shown in Fig. 2.10. It is observed that the electrolytic capacitor  $C_{elec}$  produces a square waveform due to its large ESR. On the other hand the polyester capacitor  $C_{poly}$  produces an exponential waveform due to its small ESR even with a larger capacitance value.

Table 2.3: Tested Capacitors

Voltage

450V

Material

Aluminium (Electrolytic)

ESR

$11\Omega$

Figure 2.10: Measured current waveform on the capacitors

# 2.6.3 Experimental results

The number of levels of the converter  $N_c$  are varied between 1 and 7. For SLT and DLT only even numbers are used. Figs. 2.9(a), (b) and (c) show the elevation ratio N with  $I_{out} = 0mA$  for the three topologies.

Output current is set to 50mA and 100mA by a variable resistive load. The experimental output resistance of the converter  $R_{out}$  is calculated for both currents, and then, the average value is computed. Figs. 2.9(d), (e) and (f) show a comparison of theoretical, simulation and experimental results of the output resistance  $R_{out}$  using the capacitor  $C_{elec}$  for the three topologies. This procedure is also carried out using the capacitor  $C_{poly}$  (Figs. 2.9(g), (h) and (i)).

The experimental results in Fig. 2.9 show that the theoretical analysis is consistent with the experimental and simulation results. However, for the capacitor  $C_{poly}$ , a larger error is presented due to the exponential current waveform. Both current waveforms (exponential and square), have the same average in order to satisfy the charge balance on the capacitor. It can be seen that the exponential waveform has a higher AC component and therefore, a higher RMS. In the parasitic resistances, the losses are proportional to the RMS of the current, with higher losses for the exponential waveform. This can be observed for  $C_{elec}$  in Fig. 2.9(d), where the error between the theoretical and experimental results with  $N_c = 7$  is less than 5%, whereas for  $C_{poly}$  the error is 17% (see Fig. 2.9(g)).

Despite the higher error of  $C_{poly}$ , for all the other topologies the output resistance is significatively less with this capacitor (see for SLT Figs. 2.9(e) and (h), for DLT Figs. 2.9(f) and (i)). For  $N_c = 6$  the output resistance with  $C_{elec}$  is over 2000 $\Omega$  for SLT and DLT. However, with  $C_{poly}$  is under 800 $\Omega$  for the same two topologies.

For the capacitor  $C_{elec}$ , the value of the converter gain N is slightly reduced with the increase of the number of cells. This is mainly due to the switching losses. Since the current waveform is square, the switches are turned off with a higher current value than for an exponential waveform, producing higher switching losses. For SLT and DLT, this effect is reduced (see Figs. 2.9(a), (b) and (c)).

The results show that in general the capacitor  $C_{poly}$  produces less output resistance due to its lower ESR for the three topologies. Furthermore, with no load the capacitor  $C_{poly}$  does not produce voltage drop.

# 2.6.4 Topology comparison

#### Output resistance $R_{out}$

Fig. 2.11 shows a comparison of the experimental results for the three topologies with the capacitor  $C_{poly}$ . DLT shows, in general, less output resistance than the other two topologies. This is more noticeable for the capacitor  $C_{poly}$ , since in this case, a greater percentage of the value of  $R_{out}$  is due to the switches resistance  $R_s$ . For  $C_{elec}$ , DLT also shows less output resistance the the other two topologies (see Figs. 2.9(d), (e) and (f))

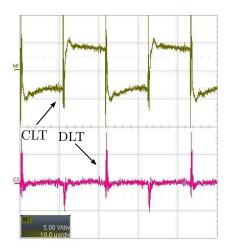

#### Output voltage ripple

Fig. 2.12 shows the measured voltage output ripple of CLT and DLT, as it is shown in the previous sections one of the advantages of DLT is the low voltage ripple. For SLT the voltage ripple is the same as for DLT, nevertheless SLT produces more voltage drop.

Figure 2.11: Comparison of experimental results for the three topologies using  $C_{poly}$

Figure 2.12: Output voltage ripple of CLT and DLT with  $N_c = 4$ ,  $V_{out} = 100V$ and  $I_{out} = 100mA$

# 2.7 Conclusions

In this chapter three different DC/DC topologies of the ladder multilevel converter were analyzed. A mathematical calculation of the gain and the output resistance for each one of the three topologies were carried out. In order to validate the theoretical analysis a prototype circuit was implemented, and simulations were performed. It was shown that the mathematical expressions are consistent with the experimental and simulation results and they can be used as a design criterium.

It was demonstrated that the DLT, presented in this chapter reduces the output resistance compared with the other two topologies, leading to less losses. Also other advantages were mentioned, such as low input current ripple and low output voltage ripple. Nevertheless, since the outputs for SLT and DLT do not have the same reference as the input, it is difficult to measure the output variables, either current or voltage. In a high voltage application, the differential voltage between the outputs and the input reference can be several kilovolts, requiring high voltage isolation sensors.

The capacitors that produce less losses are those with small ESR and conse-

quently small time constant  $\tau$ . In general the polyester capacitors have smaller ESR producing better results than electrolytic capacitors. However, a smaller time constant implies a higher current spike on the capacitors and switches which needs to be considered on the selection of these components.

As a future work, the dynamics of the converters will be studied, also control laws will be designed for the DLT converter in a glow discharge application [59].

# Chapter 3

# An Equivalent Continuous Model for Switched Systems

# 3.1 Introduction

Recently, new switched systems have been proposed for applications such as IC power converters and low distortion inverters [20, 8]. Some of these systems present fast dynamics, and the classical averaging technique cannot be used. Moreover, classical converters with a triangle ripple waveform, at low switching frequencies, present exponential ripple waveform, thus the technique in [41, 42] leads to inaccurate modeling. An alternative numerical technique that is able to model the system with an arbitrary ripple waveform is proposed in [60]. This chapter aims to analytically compute an equivalent continuous model for any switched system described by several LTI systems regardless of the speed of its dynamics. Equivalent state space matrices are obtained with analytical calculations conserving the nonlinearities related with the manipulable variables of the original system. In order to make it suitable in a general case, the method is presented for a class of switched systems with N modes. Analytical calculations for a special case of a boost power converter, which is described by two modes, are carried out.

The ripple waveform influences directly not only the average, but also the RMS value [61]. This value is directly related to the electric power dissipated by a resistive element in power electronics applications [22, 9, 1], which allows to estimate the power losses on transient and steady state. An RMS value calculation using the dynamics of the generalized equivalent continuous model, also enounced in this chapter, is proposed and validated.

The following notation and terminology will be used: All vectors are column vectors. If x is a vector,  $x^T$  is its transpose.  $\langle x \rangle$  and  $||x||_{RMS}$  are the average and RMS value of each element of vector x respectively. If A is a matrix, diag(A) represents a vector that has the diagonal elements of A, ker(A) is the null space of A. I is the identity matrix.

# 3.2 Classical Average Model and Problem Formulation

Let a switched system be described by N individual LTI subsystems

$$\dot{z} = \mathcal{A}_{\sigma} z + \mathcal{B}_{\sigma} u ,$$

(3.1a)

$$y = \mathcal{C}_{\sigma} z + \mathcal{D}_{\sigma} u \,, \tag{3.1b}$$

where  $\sigma \in [1, N] \subset \mathbb{Z}^+$ , N is the number of subsystems (modes),  $\mathcal{A}_{\sigma} \in \mathbb{R}^{\nu \times \nu}$ ,  $\mathcal{B}_{\sigma} \in \mathbb{R}^{\nu \times \mu}$ ,  $\mathcal{C}_{\sigma} \in \mathbb{R}^{d \times \nu}$ ,  $D_{\sigma} \in \mathbb{R}^{d \times \mu}$ ; with  $z \in \mathbb{R}^{\nu}$  the state vector and  $y \in \mathbb{R}^d$  the output vector.

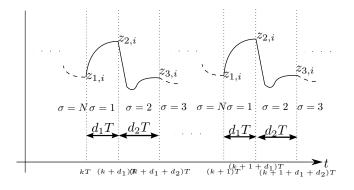

**Assumption 1.** The system follows the mode sequence  $\sigma = 1, \sigma = 2, \sigma = 3, \ldots, \sigma = N$ , and the  $\sigma^{th}$  subsystem is ON for  $d_{\sigma}T$  units of time (see Fig. 3.1).

In the previous assumption T represents the duration of the whole sequence, also called the period of one switching cycle.  $d_{\sigma}$  is then the fraction of period in which the system stays in mode  $\sigma$ . Furthermore,

$$\sum_{\sigma} d_{\sigma} = 1 \tag{3.2}$$

must be satisfied.

The average of vector  $\dot{z}$  can be written as

$$\langle \dot{z} \rangle = \frac{1}{T} \int_{t}^{t+T} \left( \sum_{\sigma} \mathcal{A}_{\sigma} z + \mathcal{B}_{\sigma} u \right) d\tau$$

(3.3)

and the average of the output vector y as

$$\langle y \rangle = \frac{1}{T} \int_{t}^{t+T} \left( \sum_{\sigma} C_{\sigma} z + \mathcal{D}_{\sigma} u \right) d\tau \,. \tag{3.4}$$

Figure 3.1: Switched system  $S, k \in \mathbb{Z}^+$  and  $z_{\sigma,i}$  is the initial condition of the state vector of subsystem  $\sigma$

The classical average model, proposed in [53], approximates the dynamics of the system, described by the transition state matrix  $e^{A_{\sigma}t}$ , with the first

constant term of its series expansion  $\langle e^{A_{\sigma}t} = I + A_{\sigma}t + \cdots \rangle$ ; this implies that the variations in the state vector through time must be slow compared with the value of T to verify the approximation. Besides, it is supposed that the input vector u has slow variations compared to the duration of one switching cycle. This approximation implies that (3.3) and (3.4) lead to the following results:

$$\langle \dot{z} \rangle = \sum_{\sigma} (\mathcal{A}_{\sigma} \langle z \rangle + \mathcal{B}_{\sigma} u) d_{\sigma} ,$$

(3.5a)

$$\langle y \rangle = \sum_{\sigma} (\mathcal{C}_{\sigma} \langle x \rangle + \mathcal{D}_{\sigma} u) d_{\sigma} .$$

(3.5b)

Notice that  $d_{\sigma}$  is multiplying each vector field. This is an approximation of the real average model and it is a technique which is widely used in order to model power converters and obtain an equivalent linear system to easily design a control law [33, 1, 62, 63].

Suppose that each subsystem of the switched system (3.1) has dynamics as fast as (or even faster than) the duration of the sequence. Thus, the state transition matrix cannot be approximated as mentioned before and the model (3.5) will not represent the average behavior of the switched system (3.1). The problem that is addressed in this chapter is the following:

**Problem 1.** Find an equivalent continuous model of the switched system (3.1) which describes its average dynamics regardless of the ratio between the variations in the state vector and the value of the duration of one switching cycle.

# 3.3 General Equivalent Continuous Model

In order to consider the whole system dynamics, it is necessary to calculate the average of vector  $\dot{x}$  considering the complete state transition matrix  $e^{\mathcal{A}_{\sigma}t}$ for each subsystem. In contrast to the classical average model, for this analysis no approximation of this matrix is carried out. In the next subsections the mathematical procedure for the calculation of the general average model is explained.

#### 3.3.1 Model

In order to simplify the analysis of the mathematical procedure, a new state space vector x be constructed as follows:

$$x = \begin{bmatrix} z^T & u^T \end{bmatrix}^T . \tag{3.6}$$

Therefore, the new system matrices are

$$A_{\sigma} = \begin{bmatrix} \mathcal{A}_{\sigma} & \mathcal{B}_{\sigma} \\ 0 & 0 \end{bmatrix}, \qquad C_{\sigma} = \begin{bmatrix} \mathcal{C}_{\sigma} & \mathcal{D}_{\sigma} \end{bmatrix}, \qquad (3.7)$$

and the system is transformed into

$$\dot{x} = A_{\sigma} x \,, \tag{3.8a}$$

$$y = C_{\sigma} x \,, \tag{3.8b}$$

where  $x \in \mathbb{R}^n$ ,  $(n = \nu + \mu)$ ,  $A_{\sigma}$  and  $C_{\sigma}$  have suitable dimensions. Notice that the dimension of the state vector x is greater than that of the original vector z.

For each subsystem  $\sigma$ , the solution of the state equation is

$$x_{\sigma}(t) = \varphi_{\sigma}(t, x_{\sigma,i}) = \phi_{\sigma}(t) x_{\sigma,i}$$

(3.9)

where

$$\phi_{\sigma}(t) = e^{A_{\sigma}t}$$

and  $x_{\sigma,i}$  is the initial condition of the state vector x for mode  $\sigma$ .

The multiplication of the  $\phi_\sigma$  matrices is carried out by the operator  $\Lambda$  which is defined as

$$\Lambda(a,b) = \begin{cases} \prod_{j=1}^{a} \phi_{b-j}(d_{b-j}T), & 1 \le a \le N \land 1 + a \le b \le N + a; \\ I, & \sim . \end{cases}$$

(3.10)

With the solution of the state equation for each subsystem, the initial condition of the state vector of subsystem  $\sigma + 1$  can be expressed as a function of the initial condition of the state vector of subsystem  $\sigma$  as

$$x_{\sigma+1,i} = \varphi_{\sigma}(d_{\sigma}T, x_{\sigma,i}).$$

(3.11)

Moreover, the initial condition of the first subsystem  $\sigma = 1$  can be expressed in terms of the initial condition of the last subsystem  $\sigma = N$  as

$$x_{1,i} = \varphi_N(d_N T, x_{N,i}).$$

(3.12)

The equivalent continuous model, which is one of the main results presented in this chapter, follows.

**Proposition 1.** Let the switched system be described by (3.8). Then, an equivalent continuous model which describes its behavior in average is

i) Dynamics of the state x

$$\langle x \rangle = \langle A \rangle \langle x \rangle, \quad \langle A \rangle = \Gamma A_c \Gamma^{-1}, \qquad (3.13)$$

where

$$A_c = \frac{1}{T} \ln(A_\delta), \qquad (3.14)$$

$$A_{\delta} = \Lambda(N, N+1), \qquad (3.15)$$

$$\Gamma = \sum_{j=1}^{N} \Omega_j \Lambda(j-1,j), \qquad (3.16)$$

and

$$\Omega_j = \frac{1}{T} \int_0^{d_j T} \phi_j(\tau) d\tau \,. \tag{3.17}$$

*ii)* Dynamics of the output y

$$\langle y \rangle = \langle C \rangle \langle x \rangle, \quad \langle C \rangle = \Gamma_C \Gamma^{-1}, \qquad (3.18)$$

where

$$\Gamma_C = \sum_{j=1}^N C_j \Omega_j \Lambda(j-1,j) \,. \tag{3.19}$$

*Proof.* Part *i*) of Proposition 1 consists of the continuous model for the state x. Using (3.11) and (3.12), the initial condition of the subsystem  $\sigma = 1$  in t = (k+1)T can be expressed as a function of the initial condition of the same subsystem in t = kT, with  $k \in \mathbb{Z}^+$  as

$$x_{1,i}((k+1)T) = A_{\delta} x_{1,i}(kT) \tag{3.20}$$

where  $A_{\delta}$  is defined in (3.15). Notice that the matrix  $A_{\delta}$  has the form

$$A_{\delta} = \begin{bmatrix} \mathcal{A}_{\delta} & \mathcal{B}_{\delta} \\ 0 & I \end{bmatrix}.$$

(3.21)

Matrices  $\mathcal{A}_{\delta}$  and  $\mathcal{B}_{\delta}$  are part of the state space model of the original vector z and its initial conditions  $z_{1,i}$ :

$$z_{1,i}((k+1)T) = \mathcal{A}_{\delta} x_{1,i}(kT) + \mathcal{B}_{\delta} u(kT). \qquad (3.22)$$

On the other hand, the mobile average of any subsystem can be expressed as

$$\frac{1}{T} \int_{t+\sum_{j=1}^{m-1} d_j T}^{t+\sum_{j=1}^{m-1} d_j T+\alpha} \varphi\left(\tau+t+\sum_{j=1}^{m-1} d_j T, x_{m_i}\right) d\tau = \frac{1}{T} \int_0^\alpha \varphi(\tau, x_{m_i}) d\tau$$

Therefore, the average of the state vector in (3.9) is

$$\langle x \rangle = \sum_{j=1}^{N} \frac{1}{T} \int_{0}^{d_j T} x_j(t) dt,$$

(3.23)

which, using (3.9), can be written as

$$\langle x \rangle = \sum_{j=1}^{N} \frac{1}{T} \int_{0}^{d_{j}T} \varphi_{j}(t, x_{j,i}) dt .$$

(3.24)

With (3.11) and (3.12), the initial conditions of subsystem  $\sigma = j$ ,  $x_{j,i}$ , can be written as a function only of the initial conditions of subsystem  $\sigma = 1$ ,  $x_{1,i}$ , using (3.10) as follows:

$$x_{j,i} = \Lambda(j-1,j)x_{1,i} \,. \tag{3.25}$$

Then (3.24) can be expressed in the form

$$\langle x \rangle = \Gamma x_{1,i} \,. \tag{3.26}$$

Now it is necessary to include the dynamics of the initial conditions of the model, and the state vector average on a continuous system. The continuous system can be obtained with a classical transformation between a discrete and a continuous system as it is indicated in (3.14).

From (3.26),

$$\langle \dot{x} \rangle = \Gamma \dot{x}_{1,i} \,. \tag{3.27}$$

Finally, with (3.26) and (3.27), the dynamics of the general average model can be written as it is shown in (3.13).

Part ii) of the proof focuses on the dynamics of y. Using (3.7), the average of the output vector y can be written as

$$\langle y \rangle = \frac{1}{T} \int_{t}^{t+T} \left( \sum_{\sigma} C_{\sigma} x \right) d\tau.$$

(3.28)

This term can be expressed as a function of the initial conditions of the model  $\sigma = 1, x_{1,i}$  and, analyzing as for the state vector x,

$$\langle y \rangle = \Gamma_C x_{1,i} \tag{3.29}$$

where  $\Gamma_C$  is given by (3.19).

With (3.26), the average of the output vector y can be expressed in terms of the average of the state vector as (3.18).

**Remark 1.**  $\Omega_j$  can be computed analytically, or numerically in the case that matrix A is singular or badly scaled.

**Remark 2.** Matrix  $\langle A \rangle$  has the form

$$\langle A \rangle = \begin{bmatrix} \langle \mathcal{A} \rangle & \langle \mathcal{B} \rangle \\ 0 & 0 \end{bmatrix}$$

(3.30)

where matrices  $\langle \mathcal{A} \rangle$  and  $\langle \mathcal{B} \rangle$  are part of the state space model of the original vector z

$$\langle z \rangle = \langle \mathcal{A} \rangle \langle z \rangle + \langle \mathcal{B} \rangle u \,.$$

(3.31)

**Remark 3.** Matrix  $\langle C \rangle$  has the form

$$\langle C \rangle = \begin{bmatrix} \langle \mathcal{C} \rangle & \langle \mathcal{D} \rangle \end{bmatrix}$$

(3.32)

where matrices  $\langle C \rangle$  and  $\langle D \rangle$  are part of the state space model of the original vector z

$$\langle y \rangle = \langle \mathcal{C} \rangle \langle z \rangle + \langle \mathcal{D} \rangle u \,. \tag{3.33}$$

It is important to notice that if the switching frequency tends to infinity, the classical average model and the model in Proposition 1 yield the same results.

# 3.3.2 Linearization

In order to easily design the control laws, an input-output linearized model is always desired. Thus, it is necessary to eliminate the nonlinearities associated with the input variables. It can be observed that matrix  $\langle A \rangle$  given in (3.13) can be written using operator  $\Lambda$  from (3.10) which is function of the state transition matrix  $\phi_{\sigma}(dT)$ . Therefore, matrix  $\langle A \rangle$  is a non linear function with respect to the input  $d_{\sigma}$ . Notice that the linearization process does not simplify the dynamics of the system in the operation point, this is the main difference with the assumption of the classical model that simplifies the state transition matrix to a constant term, simplifying its dynamics.

Let  $d_{\sigma} = \bar{d}_{\sigma} + \tilde{d}_{\sigma}$ , where  $\bar{d}_{\sigma}$  produces an operation point  $\langle x \rangle$ , i.e.  $\langle x \rangle \in$ ker  $(\langle A \rangle |_{\bar{d}_{\sigma}})$ , and  $\tilde{d}_{\sigma}$  is the increments. The linearized model can be written as follows

where

$$\begin{split} &\langle \tilde{A} \rangle = \langle A \rangle |_{\bar{d}_{\sigma}}, \quad \langle \tilde{B}_{d_{\sigma}} \rangle = \left( \frac{\partial \langle A \rangle}{\partial d_{\sigma}} \Big|_{\bar{d}_{\sigma}} \langle \bar{x} \rangle \right), \\ &\langle \tilde{C} \rangle = \langle C \rangle |_{\bar{d}_{\sigma}}, \quad \langle \tilde{D}_{d_{\sigma}} \rangle = \left( \frac{\partial \langle C \rangle}{\partial d_{\sigma}} \Big|_{\bar{d}_{\sigma}} \langle \bar{x} \rangle \right). \end{split}$$

**Remark 4.** Matrices  $\langle \tilde{B}_{d_{\sigma}} \rangle$  and  $\langle \tilde{D}_{d_{\sigma}} \rangle$  have the form

$$\langle \tilde{B}_{d_{\sigma}} \rangle = \begin{bmatrix} \langle \tilde{\mathcal{B}}_{d_{\sigma}} \rangle \\ 0 \end{bmatrix}, \quad \langle \tilde{D}_{d_{\sigma}} \rangle = \begin{bmatrix} \langle \tilde{\mathcal{D}}_{d_{\sigma}} \rangle \\ 0 \end{bmatrix},$$

where matrices  $\langle \tilde{\mathcal{D}}_{d_{\sigma}} \rangle$  and  $\langle \tilde{\mathcal{B}}_{d_{\sigma}} \rangle$  are part of the state space model of the original vector z. Remember that matrices  $\langle A \rangle$  and  $\langle C \rangle$  have the form described in remark 2 and remark 3, respectively. Therefore,  $\langle \tilde{A} \rangle$  and  $\langle \tilde{C} \rangle$  have the same form.

Since an analytical linearization is mathematically complex, it is proposed to carry out a numerical calculation that approximates the derivatives as follows:

$$\frac{\partial \langle A \rangle}{\partial d_{\sigma}} \Big|_{\bar{d}_{\sigma}} \approx \frac{\langle A \rangle |_{\bar{d}_{\sigma} + \Delta_{d_{\sigma}}} - \langle A \rangle |_{\bar{d}_{\sigma} - \Delta_{d_{\sigma}}}}{2\Delta_{d_{\sigma}}}, \qquad (3.35)$$

$$\frac{\partial \langle C \rangle}{\partial d_{\sigma}}\Big|_{\bar{d}_{\sigma}} \approx \frac{\langle C \rangle|_{\bar{d}_{\sigma} + \Delta_{d_{\sigma}}} - \langle C \rangle|_{\bar{d}_{\sigma} - \Delta_{d_{\sigma}}}}{2\Delta_{d_{\sigma}}}, \qquad (3.36)$$

where  $\Delta_{d_{\sigma}}$  is a small variation of  $d_{\sigma}$  and must be small enough in order to obtain a good approximation. This analysis can be extended to any other variable matrices  $\langle A \rangle$  and  $\langle C \rangle$  depend on.

# 3.4 RMS Value

See [47] in the attached papers.

# 3.5 Two sub models case example

In this section, results of the conventional average model and the equivalent continuous model are calculated for a typical case with only two sub models (N = 2). Also assuming  $d_1 = d$  and  $d_2 = 1 - d$ .

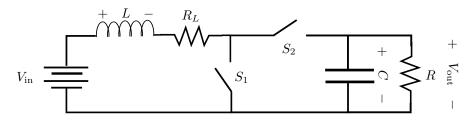

Suppose a power converter in boost configuration as shown in Fig. 3.2.  $S_1$  and  $S_2$  represent switches; L and  $R_L$  an inductance an its series resistance; C a capacitor and R the load resistance.

Figure 3.2: Boost power converter

The converter works at a constant switching frequency f. The switches  $S_1$ and  $S_2$  are complementary, and  $S_1$  is turned-on during a time equal to d/fand its complementary,  $S_2$ , during (1-d)/f. The state space variables are the inductor current  $i_L$  and the capacitor voltage  $v_C$ . The input variable is  $V_{\rm in}$ . Therefore the state space vector x and the input vector u are

$$z = [i_L \quad v_C]^T, \qquad u = V_{\rm in}.$$

(3.37)

The output of the system is the load voltage  $V_{\text{out}}$  which is equal to  $v_C$ . Thus, the state space matrices of the systems for  $\sigma = 1$  are

$$\mathcal{A}_{1} = \begin{bmatrix} -\frac{R_{L}}{L} & 0\\ 0 & -\frac{1}{CR} \end{bmatrix}, \qquad \mathcal{B}_{1} = \begin{bmatrix} \frac{1}{L}\\ 0 \end{bmatrix}, \qquad (3.38)$$

$$\mathcal{C}_{1} = \begin{bmatrix} 0 & 1 \end{bmatrix}, \qquad \mathcal{D}_{1} = 0;$$

and for  $\sigma=2$

$$\mathcal{A}_{2} = \begin{bmatrix} -\frac{R_{L}}{L} & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{CR} \end{bmatrix}, \qquad \mathcal{B}_{2} = \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix}, \qquad (3.39)$$

$$\mathcal{C}_{2} = \begin{bmatrix} 0 & 1 \end{bmatrix}, \qquad \mathcal{D}_{2} = 0.$$

The numeric values of the parameters are L = 0.1 mH,  $R_L = 5 \Omega$ ,  $C = 40 \mu$ F,  $R = 100 \Omega$ , f = 6 kHz, and d = 0.6.

# 3.5.1 Classical average model

As shown in (3.5), the classical average model can be written as

$$\langle x \rangle = (\mathcal{A}_1 d + \mathcal{A}_2 (1-d)) \langle x \rangle + (\mathcal{B}_1 d + \mathcal{B}_2 (1-d)) u, \qquad (3.40a)$$

$$\langle y \rangle = (\mathcal{C}_1 d + \mathcal{C}_2 (1-d)) \langle x \rangle + (\mathcal{D}_1 d + \mathcal{D}_2 (1-d)) u.$$

(3.40b)

Then the state space matrices are

$$\langle \mathcal{A} \rangle = \mathcal{A}_1 d + \mathcal{A}_2 (1 - d) , \qquad \langle \mathcal{B} \rangle = \mathcal{B}_1 d + \mathcal{B}_2 (1 - d) , \langle \mathcal{C} \rangle = \mathcal{C}_1 d + \mathcal{C}_2 (1 - d) , \qquad \langle \mathcal{D} \rangle = \mathcal{D}_1 d + \mathcal{D}_2 (1 - d) .$$

(3.41)

Using the numerical values of the boost converter, the matrices can be written as follows

$$\langle \mathcal{A} \rangle = \begin{bmatrix} -20 & -4 \\ 10 & -0.25 \end{bmatrix} \cdot 10^3, \qquad \langle \mathcal{B} \rangle = \begin{bmatrix} 10 \\ 0 \end{bmatrix} \cdot 10^3, \qquad (3.42)$$

$$\langle \mathcal{C} \rangle = \begin{bmatrix} 0 & 1 \end{bmatrix}, \qquad \langle \mathcal{D} \rangle = 0.$$

This model is valid only for d = 0.6.

# 3.5.2 General equivalent continuous model

Matrices  $A_{\delta}$ ,  $\Gamma$ , and  $\Gamma_C$  – from (3.15), (3.16), and (3.19) respectively – for a two sub models case are

$$A_{\delta} = \Lambda(2,3) = \phi_2((1-d)T)\phi_1(dT), \qquad (3.43)$$

$$\Gamma = \Omega_1 \Lambda(0, 1) + \Omega_2 \Lambda(1, 2), \qquad (3.44)$$

$$\Gamma_C = C_1 \Omega_1 \Lambda(0, 1) + C_2 \Omega_2 \Lambda(1, 2), \qquad (3.45)$$

where  $\Lambda(0,1) = I, \Lambda(1,2) = \phi_1(dT)$ . Using these, matrices  $\langle A \rangle \neq \langle C \rangle$  can be computed with (3.13) and (3.18).  $\langle A \rangle$  and  $\langle B \rangle$  can be decomposed using (3.30) and (3.32) respectively, leading to the following numerical results for the boost converter:

$$\langle \mathcal{A} \rangle = \begin{bmatrix} -18.72 & -3.83\\ 7.17 & -1.53 \end{bmatrix} \cdot 10^3, \qquad \langle \mathcal{B} \rangle = \begin{bmatrix} 9.32\\ 1.70 \end{bmatrix} \cdot 10^3,$$

$$\langle \mathcal{C} \rangle = \begin{bmatrix} 0 & 1 \end{bmatrix}, \qquad \langle \mathcal{D} \rangle = 0.$$

$$(3.46)$$

This model is valid only for d = 0.6. The results in (3.42) and (3.46) show a noticeable difference on the numerical values of the resulting state space matrices  $\langle \mathcal{A} \rangle$  and  $\langle \mathcal{B} \rangle$ . However, the results for  $\langle \mathcal{C} \rangle$  and  $\langle \mathcal{D} \rangle$  are equal.

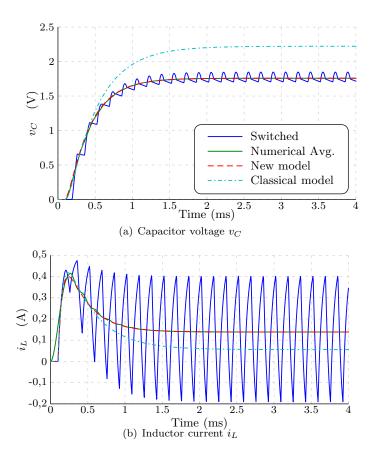

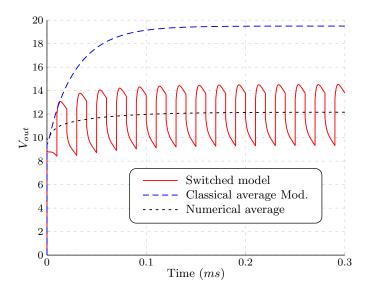

Fig. 3.3 shows the step response of the state space variables of the classical average model and the general equivalent continuous model compared with the simulated converter and the calculated average which was numerically computed in simulation. Clearly, the model proposed in this work is able to model the real converter dynamics with more accurate results than the classical average model. The classical average fails to model the DC gain of the converter for both variables,  $i_L$  and  $v_C$ . Some additional comparisons of the dynamics are performed in the next subsection.

#### 3.5.3 Linearization

Since the system dynamics dependence on parameter d is not linear, a linearization is performed. Further information on the linearization process can be found in [1].

The new input vector for the linearized system is

$$\tilde{u} = \begin{bmatrix} \tilde{V}_{\text{in}} & \tilde{d} \end{bmatrix}^T \tag{3.47}$$

Figure 3.3: Comparison of a unitary step response from  $V_{\rm in}$  to  $V_{\rm out}$

where  $V_{\rm in} = \bar{V}_{\rm in} + \tilde{V}_{\rm in}$  and  $d = 0.6 + \tilde{d}$ . The linearized model is valid only for small values of  $\tilde{d}$  and  $\tilde{V}_{\rm in}$ , i.e  $\tilde{d} \ll 0.6$  and  $\tilde{V}_{\rm in} \ll \bar{V}_{\rm in}$ .

Matrix  $\langle \tilde{\mathcal{B}} \rangle$  is an expanded version of  $\langle \mathcal{B} \rangle$  with the result of the linearization  $\langle \tilde{\mathcal{B}}_{d_{\sigma}} \rangle$ , i.e  $\langle \tilde{\mathcal{B}} \rangle = [\langle \mathcal{B} \rangle \quad \langle \tilde{\mathcal{B}}_{d_{\sigma}} \rangle].$

#### Classical average model

The numerical results of the linearized system (3.40) are

$$\langle \tilde{\mathcal{A}} \rangle = \begin{bmatrix} -20 & -4\\ 10 & -0.25 \end{bmatrix} \cdot 10^3, \qquad \langle \tilde{\mathcal{B}} \rangle = \begin{bmatrix} 10 & 22.22\\ 0 & -1.39 \end{bmatrix} \cdot 10^3,$$

$$\langle \tilde{\mathcal{C}} \rangle = \begin{bmatrix} 0 & 1 \end{bmatrix}, \qquad \langle \tilde{\mathcal{D}} \rangle = 0.$$

(3.48)

#### General equivalent continuous model

The linearization of the system described by the matrices in (3.13) and (3.18) with (3.43), (3.44), and (3.45) is performed as proposed in Section 3.3.2 with

$\Delta_d = 1$  m, leading to the following results:

$$\langle \tilde{\mathcal{A}} \rangle = \begin{bmatrix} -18.72 & -3.83 \\ 7.17 & -1.53 \end{bmatrix} \cdot 10^3, \qquad \langle \tilde{\mathcal{B}} \rangle = \begin{bmatrix} 9.32 & 17.07 \\ 1.70 & 1.21 \end{bmatrix} \cdot 10^3,$$

$$\langle \tilde{\mathcal{C}} \rangle = \begin{bmatrix} 0 & 1 \end{bmatrix}, \qquad \langle \tilde{\mathcal{D}} \rangle = 0.$$

(3.49)

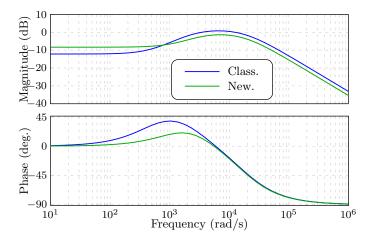

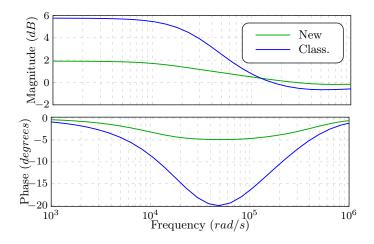

Fig. 3.4 shows the Bode diagram for the transfer function  $V_{\rm out}/V_{\rm in}$  for the classical model and the general equivalent model. It is shown that the general equivalent model has a higher gain value at low frequencies but a lower one at high frequencies. Also, the classical model produces a higher phase variation raising up to  $45^{\circ}$ .

Figure 3.4: Comparison of Bode diagrams of the transfer function  $V_{\rm out}/V_{\rm in}$

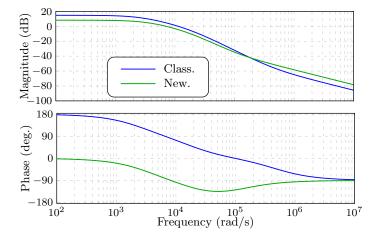

Fig. 3.5 shows the Bode diagram for the transfer function  $V_{\rm out}/d$  for the classical model and the general equivalent model. Although the magnitude is similar, the classical model produces a higher gain noticeable at low frequencies. A remarkable difference is found in phase: notice that the classical average model has a non-minimum phase zero, and the general equivalent continuous model has minimum-phase zero almost at the same frequency. Also, the classical model has a 180° inversion. This differences affect the dynamical behavior of the system and affect the stability and performance of a closed loop control law.

#### $3.5.4 \quad RMS$

See [47] in the attached papers.

# 3.6 Conclusion

In this chapter, a complete analytical calculation of a new equivalent continuous model and RMS value computation for switched systems was proposed. The models were validated with a boost power converter example showing their improvement and differences compared to the classical average model. This model can be applied to any switched system.

Figure 3.5: Comparison of Bode diagrams of the transfer function  $V_{\rm out}/d$

The proposed numerical linearization method worked well for the example exposed. On the other hand, some problems were found during the numerical computation of the model with the logarithm of  $A_{\delta}$  on the conversion from discrete to continuous. Also, if the matrices  $A_n$  are singular, the numerical calculation of  $\Omega_n$  produces some inaccuracies.

# Chapter 4

# Comparison of Robust Control Laws for a DC/DC Classical Ladder Multilevel Converter (CLT)

# 4.1 Introduction

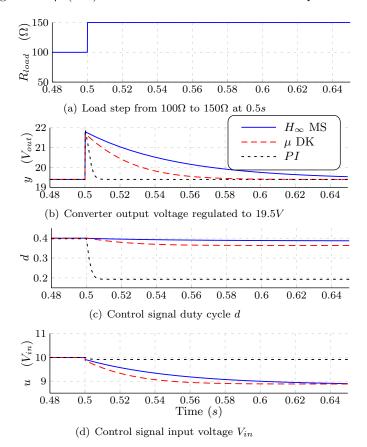

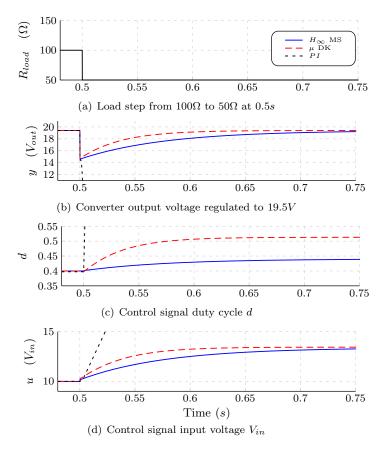

[64], [65], [66], have designed control laws for a classical clamping- capacitors multilevel structures. However this converter requires a very complex control [62]. This chapter deals with a particular multilevel voltage elevator topology which was proposed in [50]. This converter requires less control signals, switches and capacitors compared to the other multilevel topologies. Thus, its design and control is easier. The goal of this converter is to maintain a constant voltage even if the load changes. In this chapter, robust control laws are designed considering the load as an external disturbance in the model. Moreover, the performance of the control laws are compared in simulation. The results show that the  $\mu$  (DK) controller has the best response with respect to load changes. The classic *PI* control works better for nominal parameters. This chapter presents shortly the design of the control laws.

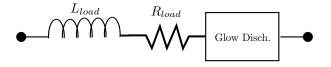

### 4.2 Classical Ladder Multilevel converter CLT

The manipulable variables of the converter (see Fig. 2.8) are: the duty cycle d, where  $HC_1$  switches are ON the first half of the cycle  $(d/f_s)$ , and  $HC_2$  switches are their complementary, where  $f_s$  denotes the switching frequency of the converter which is constant; and the input voltage  $(V_{in})$ . The main objective of the control system is to regulate the output voltage, maintaining its value under load and operating point changes. In order to regulate the voltage, any of the two input variables mentioned above can be used.

#### 4.2.1 Model parameters

The assumed parameters of the multilevel converter are: number of levels ( $N_c = 3$ ); switching frequency  $f_s = 50kHz$ ; switches ON resistances  $R_{sx} = 1\Omega$ ; capacitors  $C_x = 1\mu F$ ; capacitors  $ESR = 1\Omega$ ; load resistance  $R_{load} = 100\Omega$ ; input voltage  $V_{in} = 10V$ ; load current  $I_{load}$ . All these values are nominal and are taken from an implemented design of a ladder multilevel converter.

# 4.3 Steady State Analysis

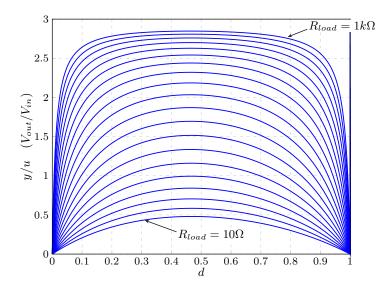

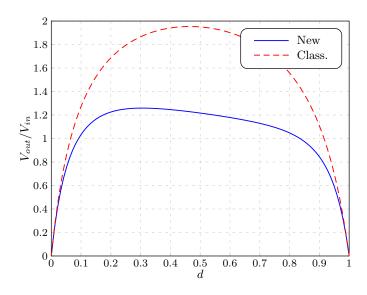

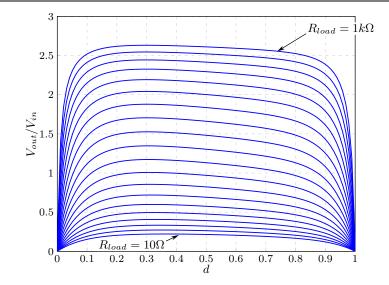

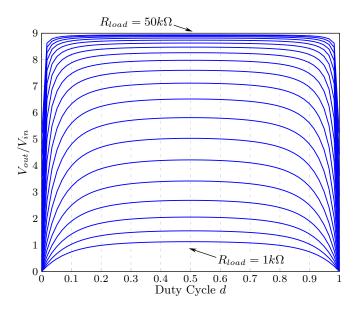

In order to decide the operational region of the converter for the control law, a steady state analysis is performed. From this analysis some conclusions about the stability and power transfer ratio of the converter are carried out and a region of operation for the control is chosen. With a state space model of the multilevel converter the relation between the input u and the output y in steady state is described by

$$0 = \langle A \rangle \langle x \rangle + \langle B \rangle u$$

$$y = \langle C \rangle \langle x \rangle + \langle D \rangle u$$

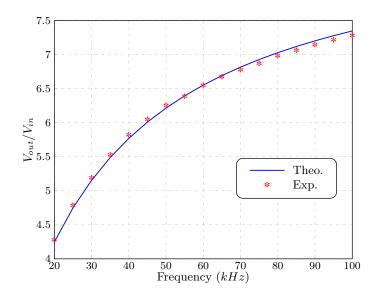

(4.1)

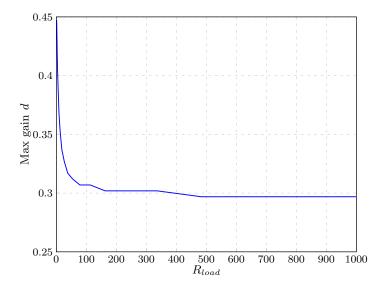

The relation y/u for different values of  $R_{load}$  was obtained as shown in Fig. 4.1. This relation is strongly dependent of  $R_{load}$ , varying the maximum gain of the converter between 0.4 and 2.7. Gains less than 1 can be achieved when the capacitors are set to a negative voltage due to the voltage drop on the resistances. However the duty cycle of maximum gain for each  $R_{load}$  is almost constant as

Figure 4.1: DC gain of the converter for different values of  $R_{load}$

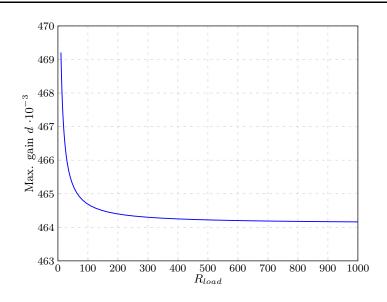

shown in Fig. 4.2. Due to the change in the slope sign of the converter gain after the duty cycle of maximum gain, the controller could lead to instability if that duty cycle is reached, nevertheless a high gain of the converter from y/u is needed. Therefore, work near the maximum gain point is necessary.

Figure 4.2: Duty Cycle of maximum gain for different values of  $R_{load}$

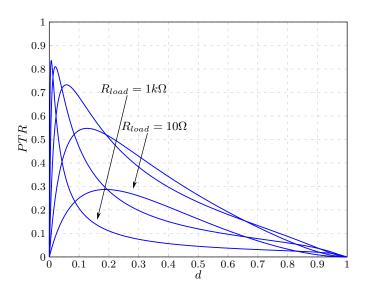

Fig. 4.3 shows the power transfer ratio  $PTR \ (P_{out}/P_{in})$  of the converter for different values of  $R_{load}$ . The higher PTR is found for d < 0.5, thus the operating point for the duty cycle is chosen to d = 0.4.

Figure 4.3: Power transfer ratio  $PTR \ (P_{out}/P_{in})$  of the converter for different values of  $R_{load}$

# 4.4 Masks

#### 4.4.1 Uncertainty masks

Three uncertainty masks are constructed, these masks are used to consider other dynamics of the converter outside the nominal values and to design a controller that meets stability, and also performance characteristics for parameters outside nominal values.

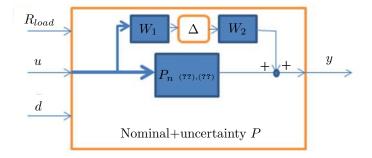

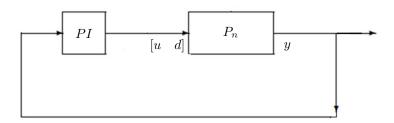

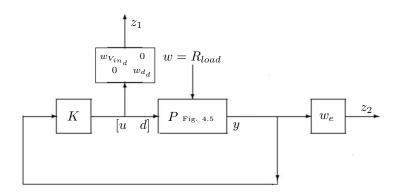

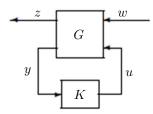

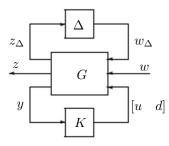

An additive non structured uncertainty was constructed as shown in Fig. 4.5, where

Figure 4.4: Uncertainty masks  $W_1$

Figure 4.5: Uncertainty model  $P(P_n \text{ is the nominal converter})$

$\Delta$  is an 1x3 matrix and represents all the possible uncertainties such that  $\|\Delta\|_{\infty} \leq 1$ . In order to construct the mask  $W_1$  the parameters  $R_{load}$ , d and  $V_{in}$  are varied over their nominal values as follows:  $R_{load} = 100\Omega \pm 50\Omega$ ,  $d = 0.4 \pm 0.06$ ,  $V_{in} = 10V \pm 5V$ .

For each mask  $w_{R_{load}}$ ,  $w_{Vin}$  and  $w_d$ , the variation on all the parameters are taken in account. The mask  $w_{Vout}$  represents the maximum variation of the output voltage y over its regulation point and was set to  $w_{Vout} = 3V$ .

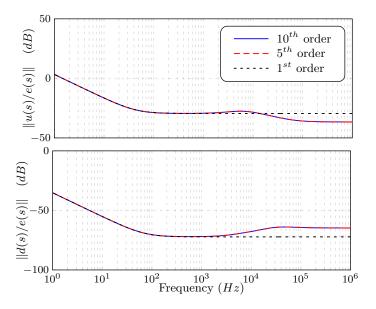

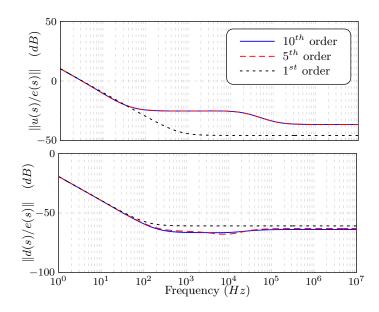

All the masks are computed taking the difference between the transfer function of the nominal converter and the converter with non-nominal values, and then, finding a 1st order transfer function that covers all the possible differences between the nominal and the non-nominal converter. The results are shown in Fig. 4.4, and show that the transfers functions  $y/R_{load}$  and y/d are considerably affected by the uncertainty, varying its gain from -10dB to 20dB.

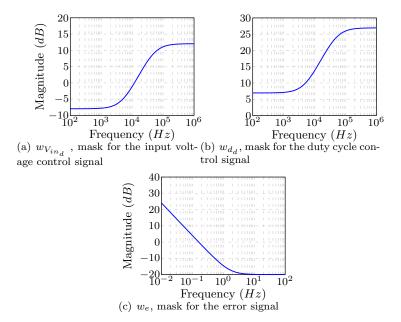

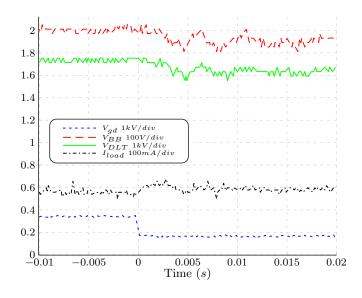

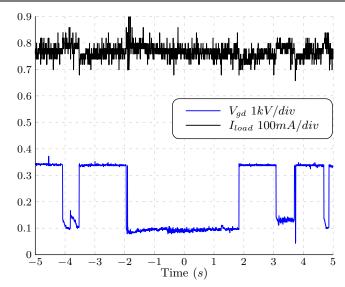

#### 4.4.2 Performance masks